Documents

Documents

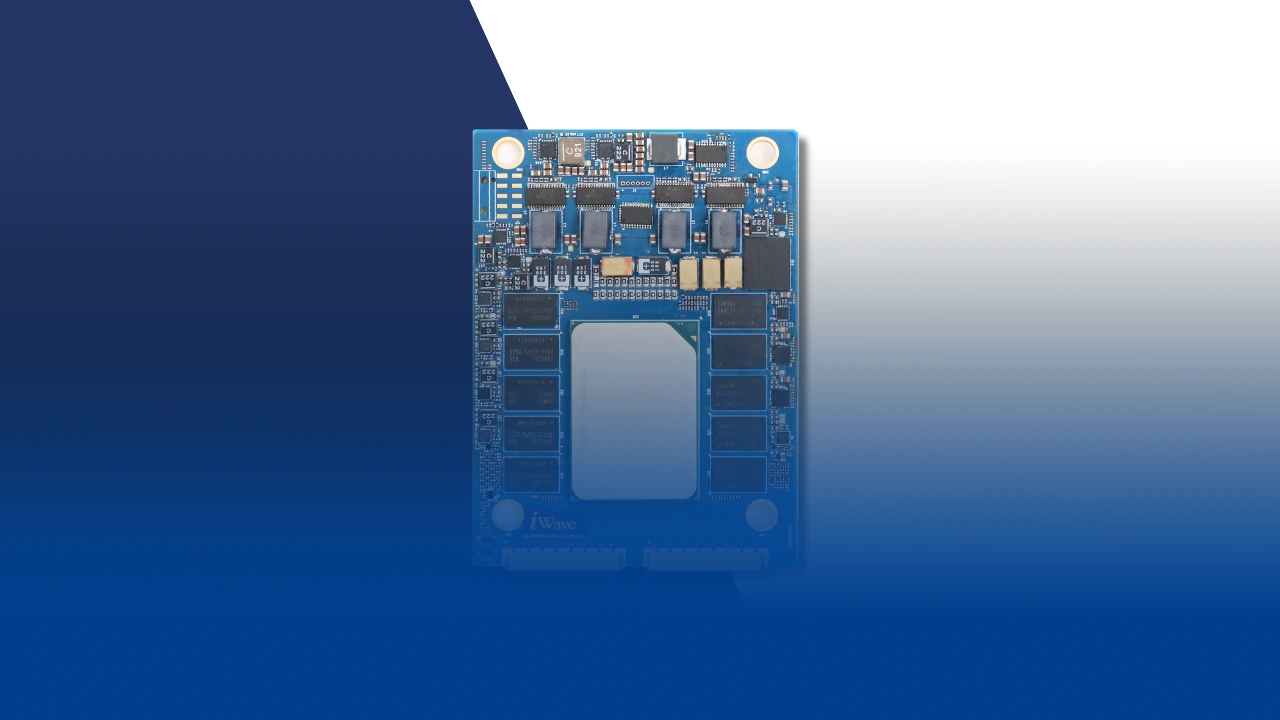

| Features | Details |

|---|---|

| Agilex 5 B32A SoC FPGA | Hard Processing System (HPS)

Field Programmable Gate Array (FPGA)

|

| RAM Memory | HPS: 32Bit 2GB LPDDR4 for HPS FPGA: 2 x 32Bit 2GB LPDDR4 for FPGA |

| On Board Flash | 32GB eMMC (Expandable) and 1Gb QSPI Configuration flash Micro SD Slot (Optional) Single 2Gb QSPI to MAX 10 for Agilex Image 1Gb QSPI to MAX 10 for NIOS FW |

| Host Interface | PCIe Gen4 x 4 |

| Expansion | FMC+ Connector (8x High Speed Transceiver Lanes) |

| MIPI CSI Connector | 4 Lane MIPI CSI Interface |

| Display Interface | 2 Lane DP Type-C Interface |

| IO Interface | 20 Pin GPIO Header 2 x PMOD Connectors USB3.0 Type-C |

| BMC | On Board BMC with:

|

| Network Interface | Front Panel QSFP+ Cage 25GbE Ethernet Ethernet 2.5G Ethernet RJ45 MagJack (FPGA) 1G Ethernet RJ45 MagJack (HPS) |

| High Performance Storage | M.2 NVMe Slot with PCIe Gen4 x 4 interface |

| Time Synchronization | Microchip ZL30733 IEEE 1588v2 1 PPS Input/Output through front panel SMA 10MHz Clock Input through front panel SMA SyncE Phase & Frequency Synchronization |

| Debug | USB TypeC Debug Port for HPS in Front Panel Dual Stack LED in Front Panel |

| Thermal | Single width Active cooling (by default) Single width Passive cooling (Optional) |

| Operating Temperature | -40°C to +85°C (Industrial) |

| Power | 75W max from PCIe x 4 Host 8Pin ATX Power Connector in Back Panel Power Droop Sharing (to maximise power when needed) Power dissipation is application dependent |

| Form Factor | 167.65mm x 98.40mm (Half Length PCIe) |

| Compliance | RoHS Compliant REACH Compliant |