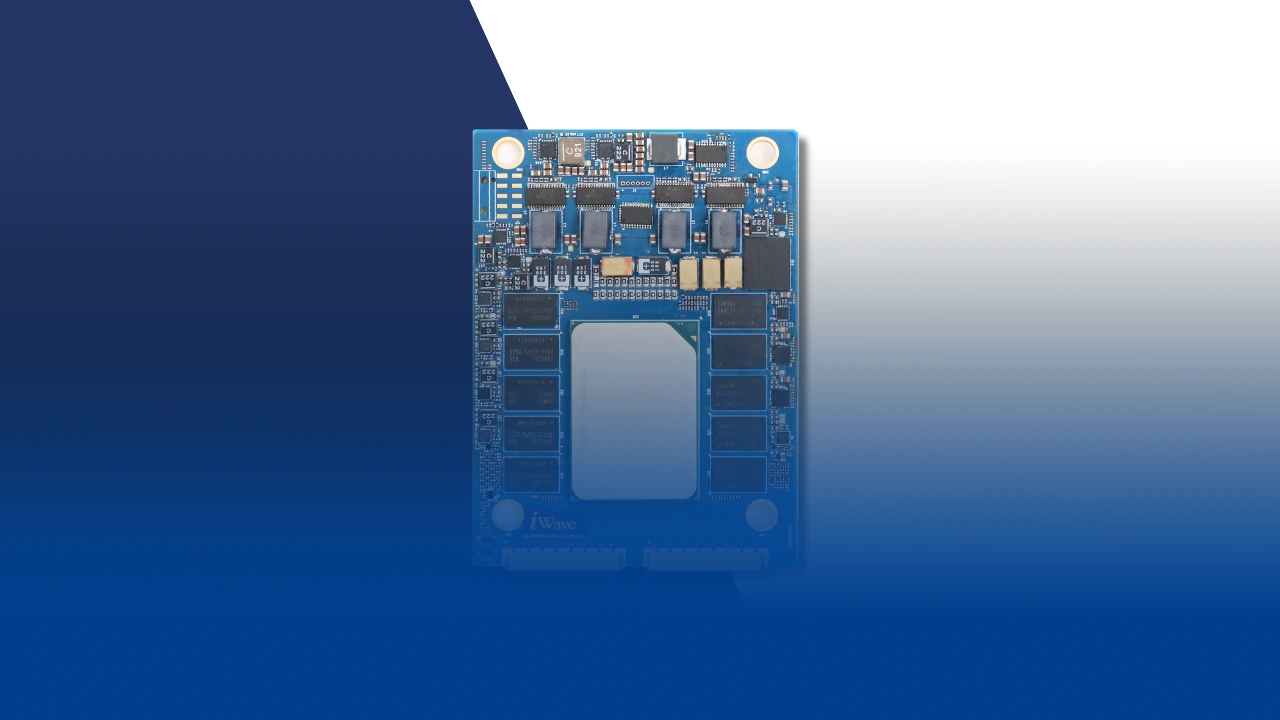

| PCIe NIC Card |

- 254mm x 111.15mm, 3/4 Length, Full Height, Dual Slot with Active Cooling PCIe Card.

- Intel Agilex 7 I-Series FPGA

- Speed Grade: -1 (Transceiver) and –2 (Core)

- 3 x F-Tiles and 1 x R-Tile Transceiver Tiles

- 48 x FGT Transceivers upto 58Gbps

- 8 x FHT Transceivers upto 116Gbps

- 16 x R-Tile Transceivers upto 32Gbps for PCIe

- 4.1M Logic elements

- 287 Mb Embedded Memory

- PCIe Gen5 x16 Host Interface

- SKU1: Dual QSFP56-DD Cages (400GbE/200GbE)

- Line Rates: 1 x 400G, 2 x 200G, 4 x 100G, 8 x 50G, 2 x 40G, 8 x 25G, 8 x 10G

- SKU2: QSFP112-DD Cages (800GbE/400GbE)

- Line Rates: 2 x 400G, 4 x 200G, 8 x 100G, 8 x 50G, 8 x 25G

- Dual SMA Connectors

- NVMe Slot – Gen 4 x4 for Storage media over M.2

- Three DDR4 Channels

- HPS – Single 8GB, 72b, 3200MHz @409.6 Gbps

- FPGA – Dual 16GB, 72b, 3200MHz @409.6 Gbps

- SlimSAS Connector – Dual PCIe Gen 4 x8

- Quad Core ARM Cortex A53

- Single USB 2.0

- 1G Ethernet RJ45

- 20 pin GPIO for I2C, SPI

- Max10 Board Management Controller

- Voltage, Current and Temperature Monitoring

- Field Updates of FPGA (Partial reconfiguration)

- FPGA Configuration and Control

- I2C Bus access

- Voltage Overrides

- Storage Media

- Single 1Gb QSPI to Agilex

- Single 2Gb QSPI to MAX 10 for Agilex Image

- 1Gb QSPI to MAX 10 for NIOS FW

- 32GB HPS eMMC

- Single Micro SD Slot for HPS

|

| OFS FIM |

- Line rates with F-Tile Ethernet:

- 400G – 4 x 100G or 8 x 50G

- 200G – 4 x 50G or 8 x 25G

- PCIe: F-tile PCIe Gen5x16

- PCI Capabilities: SR-IOV, ACS, Data Link

- Hard Processor System (HPS) with 8GB DDR4, x72 (with ECC),

3200 MHz, 8GB with a max throughput of 409.6 Gbps.

- Virtualization: 5 physical functions/3 virtual functions with ability to expand.

- Memory: Two Fabric DDR4 channels, x72 (with ECC), 3200 MHz, 8GB with a max throughput of 409.6 Gbps.

- BMC:

- Voltage, current, temperature monitoring and reporting.

- FPGA configuration over AVSTx8

- BMC as Root of Trust

- Supports secure remote system update (RSU) through PCIe

For more information on Intel OFS refer the following Link – https://ofs.github.io/ofs-2024.2-1/ |

| Host Server Environments |

- Server : Dell PowerEdge R760

- PCIe : Gen 5 x 16

- Disk: Free Space up to 50GB

- Memory: 128GB

- BIOS: Enable IOMMU, Hugepages, PCI Reallocation, Disable PCI-ASM

- Supported OS: Ubuntu 22.04, RedHat 8

- Supported Libraries & Applications: OPAE SDK, HE-Exerciser, LinuxPTP, DPDK

|

| OFS Software |

HE-Exerciser

- The host interacts with the FPGA using the Linux DFL (Device Feature List) and OPAE (Open Programmable Accelerator Engine) libraries https://ofs.github.io/ofs-2024.2-1/sw/fpga_api/prog_guide/FPGA-lib-1.png

- HE applications communicate with the HSSI, Loopback, Traffic Generator, and Memory modules within the AFU region of the FPGA.

- The application also extends its functionality to transmit workloads over QSFP ports at various speeds.

DPDK-IFPGA

- The DPDK based IFPGA libraries help to interact with Management modules.

- The IFPGA Rawdev Driver utilizes Intel FPGA Software Stack OPAE (Open Programmable Acceleration Engine) for FPGA management.

- Management Modules include FPGA status check, FPGA reset or reboot, PR reset, Read/Write PCI configuration space, bind or unbind FPGA with kernel drivers.

Linux PTP

- The kernel exposes ToD IP as a PTP Hardware Clock to the Linux PTP stack, allowing the system clock to synchronize with the ToD information

- The phc2sys utility to access ToD information and synchronize the system clock.

|