Documents

White Paper

| Features | Details |

|---|---|

| RoCEv2 |

|

| Highlights | RoCEv2 IP core provides RDMA over Converged Ethernet implementation in FPGA. RoCEv2 IP core provides Low latency, High throughput and is compatible with standard MAC interface |

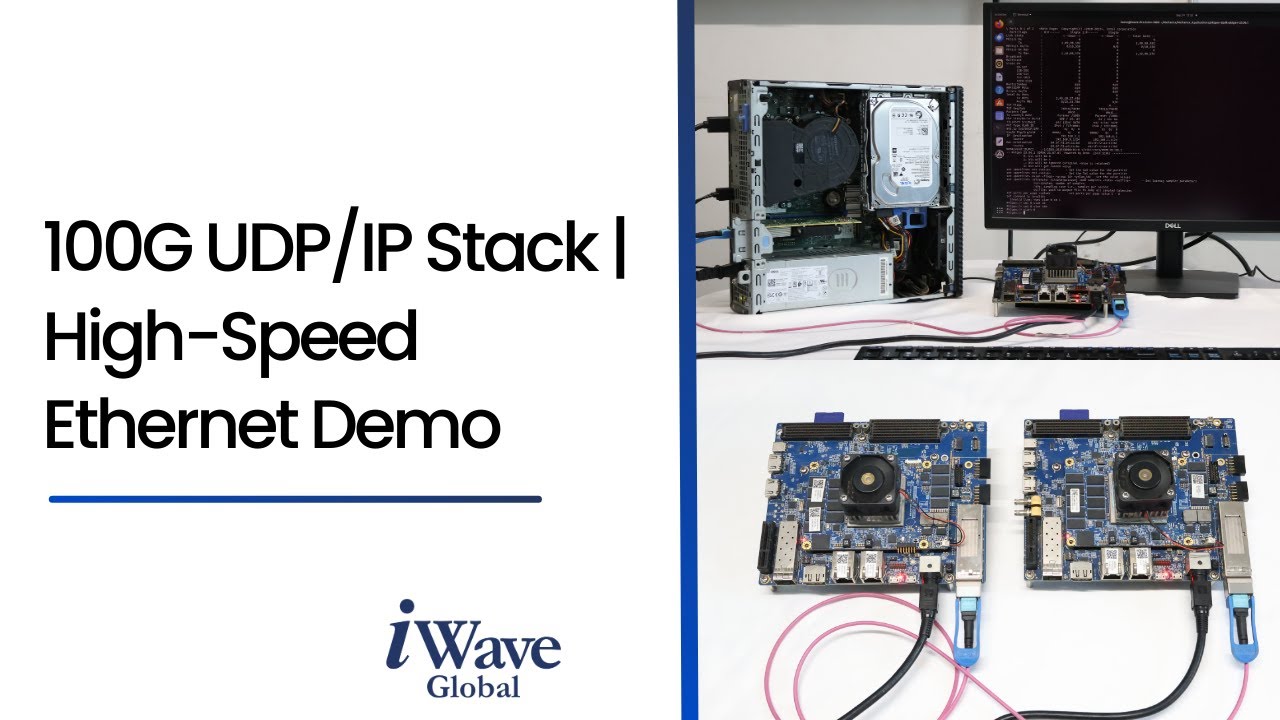

ZU11/17/19 Dev Kit

iWave 100G RoCEV2 IP core has been tested on AMD/Xilinx Zynq MPSoC FPGAs using iWave’s ZU11/17/19 based development kit. The QSFP connector on the carrier card provides a 100G Ethernet interface, enabling communication either with a host system supporting 100G RoCEV2 or with another development kit for IP evaluation.

Integration Manual