Documents

Documents

Design Support

Software

| Features | Details |

|---|---|

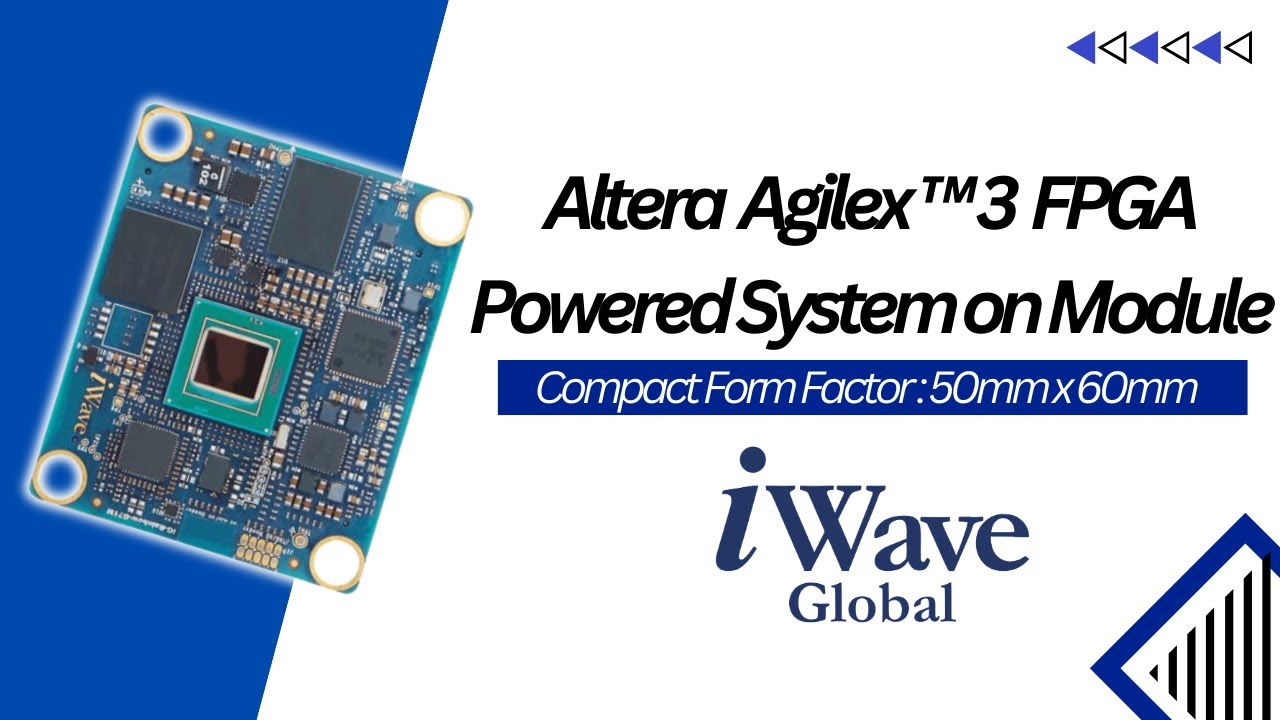

| SoC | Agilex 5 E-Series SoC FPGA Compatible Agilex 5 E-Series Package Family

Field Programmable Gate Array (FPGA)

Hard Processing System (HPS)

|

| Memory & Storage | 2GB LPDDR4 with ECC for HPS (32bit) 2 x 2GB LPDDR4 with ECC for FPGA (32bit) 32GB eMMC (Expandable up to 128GB) 1Gb QSPI Flash (Expandable up to 2Gb) EEPROM |

| IPMC | Arm® 32-bit Cortex®-M0+ CPU up to 80 MHz On chip 64KB of flash and 4KB of SRAM One 12-bit 1.68-MSPS analog-to-digital converter (ADC) |

| VPX Front Panel features | Gigabit Ethernet Header USB 2.0 & 3.0 through USB Type-C Connector 3-pin Debug UART Header Display Port ADC x4 & DAC x4; Sampling rate up to 1.6GSPS1 |

| VPX On board features | On Board Clock Generators Temperature Sensor x1 Elapse Counter x1 EEPROM x1 |

| 3U VPX Backplane: Connector – P0 |

Utility Plane

|

| 3U VPX Backplane: Connector – P1A +P1B |

Data Plane Port-01

Data Plane Port

Control Plane Port

Expansion Plane Port

System Control Signals (Maskable Reset, SYSCON, GDiscrete1, CLK1orGP) |

| 3U VPX Backplane: Connector – P2A |

Expansion Plane Port

|

| 3U VPX Backplane: Aperture Pattern J – P2B |

MT Ferrule Module – MM12F – 12 Fibre ports NanoRF -10

|

| Profile Specification | Profile: SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-4 Module Profile as per AMPS: MODA3p-16.6.13-1-4-F2C-(E8-E7) (P3F – N, 16G2) (E7) (N-G2) [E12] |

| Profile: SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-0 Module Profile: MOD3p-PAY-1F1U1S1S1U1U4F1J-16.6.13-1 Module Profile as per AMPS: MODA3p-16.6.13-1-4-F2C-(E8-E7) (P3F – N, 16G2) (E7) (N-G2) [E12] |

|

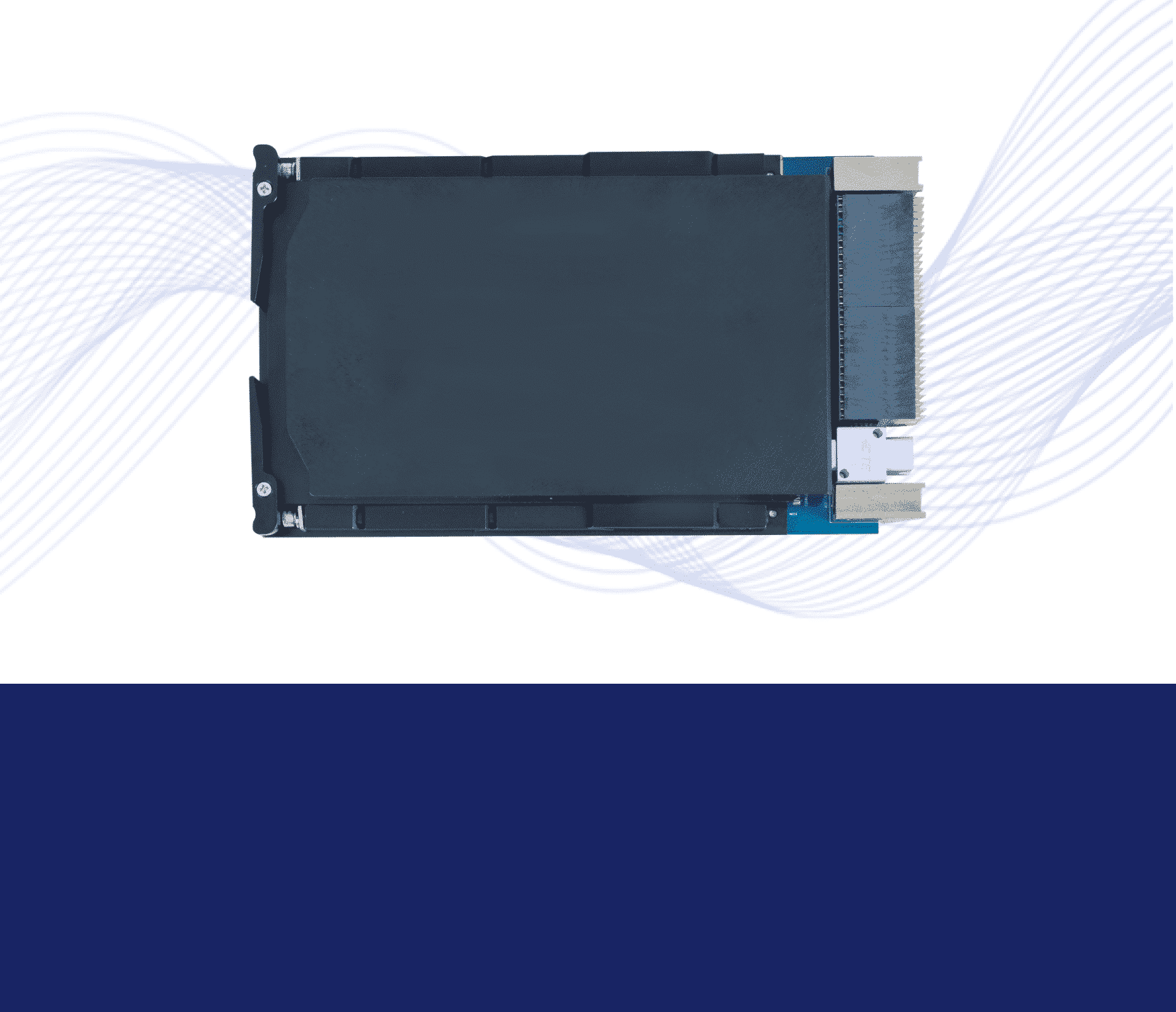

| General Specification | Slot Pitch: 1 inch Conduction Cooled BSP Support: Linux Form Factor: 160mm X 100mm Environment Specification: RoHS & REACH Compliant |

1ADC x4 &DAC x4 will be either supported in Front panel or Backplane

For any highly integrated FPGA VPX Plug-in Module, thermal design is a very important factor. iWave supports a VITA 48.2 compliant 3U Conduction Cooled Heat Spreader.